The Indian Institute of Science (IISc) will partner with Samsung Semiconductor India Research (SSIR) for research and development in the field of on-chip Electrostatic Discharge (ESD) protection.

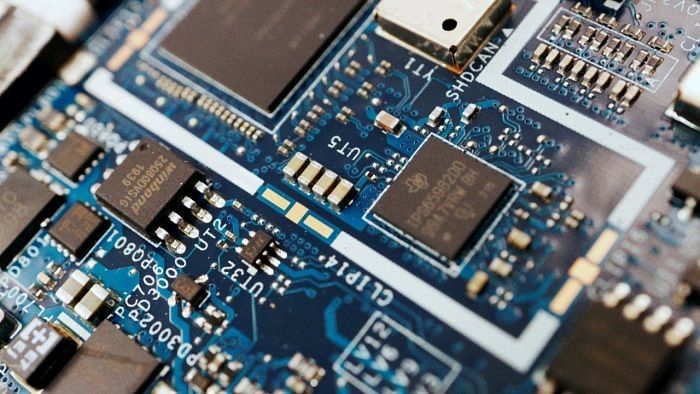

Under a research agreement, the partners propose to build cutting-edge ESD device solutions to protect ultra high speed serial interfaces in advanced Integrated Circuits (ICs) and system-on-chip (SoC) products.

IISc said on Wednesday that the related research will be carried out by Prof Mayank Shrivastava’s group at the IISc’s Department of Electronic Systems Engineering. The solutions arising from this research will be deployed in Samsung’s advanced process nodes.

ICs and SoCs, both essential to all systems, are very sensitive to ESD failures, especially those developed using advanced nanoscale CMOS (Complementary Metal Oxide Semiconductor) technologies. ESD failures contribute to most of the IC chip failures and field returns. The partnership is significant considering that R&D in ESD technology for highly reliable interfaces and SoCs that operate at low power and high speed is integral to innovation in semiconductors.

Balajee Sowrirajan, CVP and MD at SSIR, Bengaluru, said SSIR aimed to facilitate training programmes at the postgraduate level, opening up opportunities for students to pursue industry internships and encourage young researchers to become entrepreneurs.

Prof Govindan Rangarajan, Director, IISc, said the partnership “reinforced” IISc’s commitment to strengthen industry-academia engagements that can make a significant impact in the coming years.